友情提示点击顶部放大镜 可以使用站内搜索 记住我们的地址 www.hainabaike.com

原文作者:Eben Upton。参与:路雪、黄小天、李泽南

过去几天,对 Meltdown 和 Spectre 安全漏洞的讨论甚嚣尘上。该漏洞影响了所有的现代英特尔处理器,Spectre 还影响了 AMD 处理器和 ARM 内核。Spectre 漏洞使得攻击者可以绕过软件检查读取当前地址空间中的任意位置数据;Meltdown 漏洞使得攻击者可以读取操作系统核地址空间的任意位置数据(用户程序通常不可访问该数据)。这两种漏洞皆通过边信道攻击(side-channel attack)利用很多现代处理器都有的性能特征(缓存和推测执行)泄漏数据。近日,树莓派创始人 Eben Upton 称树莓派不受这些漏洞的影响,并撰文详解其原因。

谷歌 Project Zero 团队发现的漏洞分别被称为「Meltdown」和「Specter」。这些漏洞允许恶意程序从其它程序的内存中窃取信息,这意味着恶意程序可以监听密码、账户信息、密钥及理论上存储在进程中的任何内容。

其中,「Meltdown」影响英特尔处理器,它打破了用户应用程序和操作系统之间最基本的隔离。这种攻击允许程序访问其它程序和操作系统的内存,这可能导致数据泄露。而「Spectre」除了能影响英特尔处理器外,还能影响 AMD 与 ARM 架构的大量处理器,这意味着除服务器与个人电脑以外,智能手机等终端设备也会受到影响,几乎所有现代计算机处理器均无法幸免。它打破了不同应用程序之间的隔离,这意味着,攻击者可以使用恶意程序来获取被隔离的私有数据。

英特尔近日表示,在未来数周内将有软件补丁发布。尽管大多数 PC 用户不会受到影响,但安全补丁会导致处理器 0-30% 的运算速度下降。

根据Eben Upton所述,大量类似树莓派的廉价计算设备可能同样也不会受到两种安全漏洞的影响,包括很多低端安卓手机。

本文介绍现代处理器设计的一些概念,使用简单的 Python 程序解释这些概念,比如:

t = a+b u = c+d v = e+f w = v+g x = h+i y = j+k

尽管你的计算机处理器不会直接执行 Python,但这里的语句足够简单,大致相当于简单的机器指令。本文不详述过多处理器设计中的重要细节(主要是 pipelining 和寄存器重命名),它们对理解 Spectre 和 Meltdown 的工作原理不太重要。

想全面了解处理器设计和现代计算机架构,可参阅 Hennessy 和 Patterson 的经典著作《Computer Architecture: A Quantitative Approach》。

什么是标量处理器?

最简单的现代处理器每次循环执行一个指令,我们称之为标量处理器。上述示例在标量处理器上需要执行六次循环。

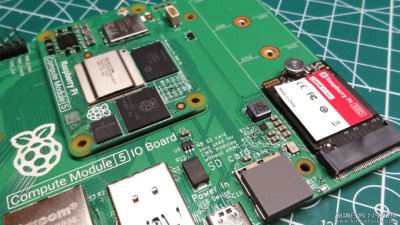

树莓派 1 和树莓派 Zero 中使用的 Intel 486 和 ARM1176 都是标量处理器。

什么是超标量处理器?

很明显,加速标量处理器的方式就是提高其时钟频率(clock speed)。但是,我们很快就到达处理器内部逻辑门运行的极限;因此处理器设计人员开始寻找一次性处理多件事情的方式。

有序超标量处理器检查收到的大批指令,尝试在一个 pipeline 中一次性执行多个指令,这取决于指令之间的依赖关系。依赖关系很重要:你或许认为双向超标量处理器可以将 6 个指令配对执行,如下所示:

t, u = a+b, c+d v, w = e+f, v+g x, y = h+i, j+k

但是这没有作用:我们必须先计算 v 再计算 w,即第三个和第四个指令无法同时执行。双向超标量处理器实际上无法找到与第三个指令配对的指令,因此,该示例将执行四个循环:

t, u = a+b, c+d v = e+f # second pipe does nothing here w, x = v+g, h+i y = j+k

超标量处理器包括 Intel Pentium 以及树莓派 2 和树莓派 3 分别使用的 ARM Cortex-A7 和 Cortex-A53。树莓派 3 的时钟频率只比树莓派 2 高 33%,但性能大约是后者的 2 倍:部分原因在于 Cortex-A53 超出 Cortex-A7 的对大量指令的配对执行能力。

什么是无序处理器(out-of-order processor)?

回到我们的示例,我们可以看到即使 v 和 w 之间存在依赖关系,我们也可以找到其他独立的指令填补第二次循环中空的 pipe。无序超标量处理器能够打乱指令的顺序(同样受限于指令之间的依赖关系)以保持每个 pipeline 都处于忙碌状态。

无序处理器可以有效交换 w 和 x 的顺序:

t = a+b u = c+d v = e+f x = h+i w = v+g y = j+k

允许执行三次循环:

t, u = a+b, c+d v, x = e+f, h+i w, y = v+g, j+k

无序处理器包括 Intel Pentium 2(以及大部分后续 Intel 和 AMD x86 处理器,除了一些 Atom 和 Quark 设备)和很多近期的 ARM 处理器,如 Cortex-A9、-A15、-A17、-A57。

什么是分支预测器(branch predictor)?

上述示例是直线式代码块。真正的程序不是这样的:他们还包括正向分支(用于实现条件运算,如 if 语句)、反向分支(用于实现 loop)。分支可能是无条件的(通常被采用),也可能是有条件的(是否采用取决于计算值)。

获取指令时,处理器可能遇到依赖于计算值的条件分支(而该值目前尚未计算出)。为了避免停顿,处理器必须猜测下一个要获取的指令:内存顺序(对应未采用分支)或分支目标(对应采用分支)上的下一个指令。分支预测器通过收集某一个分支之前被采用频率的相关统计数据,帮助处理器猜测该分支是否被采用。

现在分支预测器非常复杂,可以生成非常准确的预测。树莓派 3 的额外性能部分是由于 Cortex-A7 和 Cortex-A53 之间分支预测的改进。但是,攻击者也可以通过执行精心设计的一系列分支,误训练分支预测器作出较差的预测。

什么是推测?

重排序顺序指令(reordering sequential instruction)是一种恢复指令级别并行化的强大方法,但是由于处理器变得更宽(能够一次执行三个或四个指令),保证所有 pipeline 处于忙碌状态变得更难了。因此,现代处理器提高了推测能力。推测执行可以处理并不需要的指令:这样就可以保证 pipeline 处于忙碌状态,如果最后该指令没有被执行,我们只需要放弃结果就可以了。

推测执行不必要的指令(以及支持推测和重排序的基础架构)需要耗费大量能源,但是在很多情况下为了获取单线程性能的提升,这种方法是值得的。分支预测器用于选择通过程序最可能的路径,最大化推测获得收益的可能性。

为了展示推测的好处,我们可以看一下另一个示例:

t = a+b u = t+c v = u+d if v: w = e+f x = w+g y = x+h

现在,我们具备从 t 到 u 到 v、从 w 到 x 到 y 的依赖关系,那么没有推测的双向无序处理器无法填充第二个 pipeline。它用三次循环来计算 t、u 和 v,之后处理器知道 if 语句的主体是否被执行,然后用三次循环来计算 w、x 和 y。假设 if(由一个分支指令实现)使用了一次循环,那么该示例可以执行四次(v 是零)或七次循环(v 不是零)。如果分支预测器表明 if 语句的主体很可能被执行,那么推测可以有效打乱程序,如下:

t = a+b u = t+c v = u+d w_ = e+f x_ = w_+g y_ = x_+h if v: w, x, y = w_, x_, y_

因此现在我们有了额外的指令级别的并行来保持 pipeline 繁忙:

t, w_ = a+b, e+f u, x_ = t+c, w_+g v, y_ = u+d, x_+h if v: w, x, y = w_, x_, y_

循环计数在推测性无序处理器中变得不太明确,但是 w、x 和 y 的分支和条件更新(几乎)是空闲的,因此上述示例几近于执行三个循环。

什么是缓存?

在过去,处理器速度与内存访问速度成正比。我的 BBC Micro(2MHz 6502),可以每 2μs(微秒)执行一次指令,存储周期为 0.25μs。在接下来的 35 年中,处理器已经变的非常快,但是内存几乎没变化:树莓派 3 中的一个 Cortex-A53 可以每 0.5ns(纳秒)执行一次指令,但是可能需要 100ns 才能访问主存。

a = mem[0] b = mem[1]

需要 200ns。

但在实践中,程序倾向于以相对可预测的方式访问内存,同时展示时间局部性(如果我访问一个定位,我很可能很快再次访问它)和空间局部性(如果我访问一个定位,我很可能很快访问附近的位置)。缓存利用这些属性来降低访问内存的平均成本。

缓存是一个小的片上内存,接近于处理器,存储最近使用的位置(及其近邻)内容的副本,以便在随后的访问中可以快速获取。借助缓存,上述示例的执行将稍微超过 100ns:

a = mem[0] # 100ns delay, copies mem[0:15] into cache b = mem[1] # mem[1] is in the cache

从 Spectre 和 Meltdown 的角度来看,最重要的一点是你可以对内存访问的时间进行计时,你可以知道访问的地址是在缓存之中(短时)或者不在(长时)。

什么是边信道?

来自维基百科:

「边信道攻击是基于从密码系统的物理实现获得的信息的任何攻击,而不是算法中的蛮力或理论弱点(相较于密码分析学)。例如,定时信息、功耗、电磁泄漏甚至声音都可以提供额外的信息源,这些信息可被用来破解系统。」

Spectre 和 Meltdown 属于边信道攻击,通过定时来观察缓存中是否有另一个可访问的位置,以推断内存位置的内容,这些内容通常不应该被访问。

把它放在一起

现在让我们看看如何结合推测和缓存以允许类似 Meltdown 的攻击。考虑下面这个示例,它是一个有时读取所有非法(内核)地址的用户程序,并导致错误(崩溃):

t = a+b u = t+c v = u+d if v: w = kern_mem[address] # if we get here, fault x = w&0x100 y = user_mem[x]

现在,假设我们可以训练分支预测器,使其相信 v 很可能是非零的,那么我们的无序双向超标量处理器就会混洗程序,像这样:

t, w_ = a+b, kern_mem[address] u, x_ = t+c, w_&0x100 v, y_ = u+d, user_mem[x_] if v: # fault w, x, y = w_, x_, y_ # we never get here

即使处理器总是推测性地读取内核地址,它必须推迟产生的错误,直到知道 v 是非零。从表面上看,这是安全的,因为:

- v 是零,所以非法读取的结果不会被提交给 w

- v 是非零,但在读取结果被提交给 w 之前发生了错误

然而,假设我们在执行代码之前刷新缓存,并排列 a、b、c、d 以使 v 实际上为零。现在第三个循环中的推测性读取为:

v, y_ = u+d, user_mem[x_]

其将依赖非法读取结果的第八位获取用户地址 0x000 或 0x100,并把地址及其近邻加载进缓存。由于 v 是零,推测性指令的结果将被摈弃,执行将继续。如果我们随后访问其中一个地址,就可以决定哪个地址在缓存之中。恭喜:你刚刚从内核地址空间读取了一个位!

真正的 Meltdown 实际上要比这更复杂(特别是,为了避免错误训练分支预测器,作者无条件地优先执行非法读取,并处理产生的异常),但原理是相同的。Spectre 使用相似方法来颠覆软件阵列边界检查。

结论

现代处理器竭尽全力保持抽象,从而成为直接访问内存的有序标量机器,而事实上,使用包括缓存、指令重排序和推测在内的大量技术来提供比简单处理器更高的性能有望成为现实。Meltdown 和 Spectre 就是当我们在抽象的语境中推理安全性,然后在抽象与现实之间遇到细微差别时会发生的事情的实例。

树莓派使用的 ARM1176、Cortex-A7 和 Cortex-A53 内核中推测的缺失使我们免于此类攻击。

译文出处。

标签: 树莓派raspberrypi阅读

评论列表